**Student Paper**

## Analysis of the Biasing Conditions and Latching Operation for Si/SiGe Resonant Interband Tunnel Diode Based Tunneling SRAM

S. Sudirgo<sup>a</sup>, D.J. Pawlik<sup>a</sup>, S.L. Rommel<sup>a</sup>, S.K. Kurinec<sup>a</sup>, P.E. Thompson<sup>b</sup>, and P.R. Berger<sup>c</sup>

<sup>a</sup> Rochester Institute of Technology, Department of Microelectronic Engineering, USA, ssudirgo@mail.rit.edu

<sup>b</sup> Naval Research Laboratory, USA,

<sup>c</sup> The Ohio State University, Department of Electrical Engineering, USA

A memory cell utilizing negative differential resistance (NDR) characteristic of tunnel diodes was first proposed by Goto et al. in 1960 [1]. The inherently fast tunneling phenomenon and low power consumption makes this type of memory architecture attractive. Combined with the possibility for vertical integration of the tunnel diode directly atop of the source/drain region of the FET, a compact design can be achieved. The concept was further refined by Van der Wagt et al. to achieve low stand-by power by utilizing diode junction capacitance to lower peak and valley current densities. Utilizing InP/InGaAs resonant tunnel diode (RTD), a nA operation was realized [2]. The realization in Si-based system, however, is still limited. Utilizing p<sup>+</sup>Si/oxynitride/n<sup>+</sup>poly Si tunnel diodes, Morimoto et al. demonstrated a low voltage T-SRAM [3]. The performance was limited by the poor performance of the tunnel diode and the lack of capability to scale current density and size. In recent work by the authors, Si/SiGe resonant interband tunnel diodes (RITDs) have been successfully integrated with CMOS devices. A low voltage monostable-bistable logic element (MOBILE) latch has been demonstrated [4]. The current density of a Si/SiGe RITD is controlled by adjusting the SiGe i-layer thickness, making it suitable for circuit integration with CMOS [5]. In this work, Si/SiGe RITD-based T-SRAM cell is bread-boarded and its latching mechanisms have been investigated extensively.

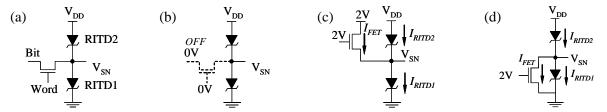

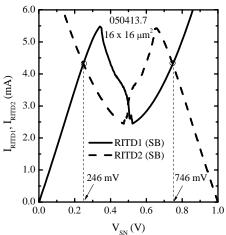

As shown in Fig. 1(a), each T-SRAM cell consists of two tunnel diodes connected in series with a current manipulator, NFET, connected into the sense node. In this experiment, Si/SiGe RITDs with 6 nm i-layer grown on top of  $p^+$  implanted wells with PVCR of 2.25 and peak current density of 2.15 kA/cm² were used. During the stand-by (SB) mode, NFET is off, and  $V_{DD}$  is fixed at 1.0V, as illustrated in Fig. 1(b). RITD1 and RITD2 function as the driver and load, respectively, resulting in folded current-voltage characteristics as depicted in Fig. 2. The intersections the drive and load curves indicate two stable latching states, stand-by low (SBL) and high (SBH) at 246 mV and 746 mV, respectively. These two states represent logic low and high, respectively. It is important to note that the intersection at the negative differential resistance (NDR) region is unstable and is not be used as a latching point.

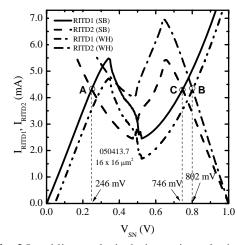

To latch into logic high, a current has to be supplied into the sense node through the NFET by applying a bias of 2.0V to both the drain and gate. Fig. 1(c) depicts the circuit diagram during this write high (WH) cycle. By activating the NFET, a current path parallel to RITD2 is formed, elevating the overall current that passes through the load diode as shown in Fig. 3. At the same time, current injection into the middle node also causes a decrease in drive current. As a result, the potential at the sense node ( $V_{SN}$ ) changes abruptly from point **A**, 246 mV, to **B**, 802 mV. By restoring the stand-by biasing conditions, i.e. shut-off the NFET,  $V_{SN}$  restores to the nearest stable latching state at 746 mV, point **C**.

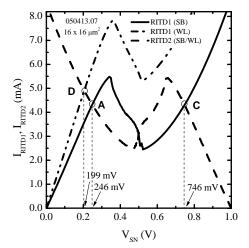

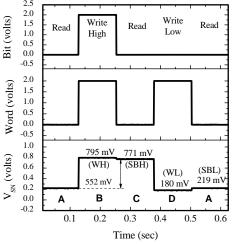

In the write to logic low (WL) cycle, current is subtracted or drained from the sense node by simply applying a bias to the gate of the NFET and grounding the bit node. Since there is a potential difference between sense and bit node, current will flow out of the sense node as illustrated in Fig. 1(d). In other words, a current path parallel to RITD1 is created, causing a rise in the drive current. Unlike the write high cycle, the load characteristic is undisturbed during WL cycle. As a result,  $V_{SN}$  changes suddenly from point  $\bf C$ , 746 mV, to  $\bf D$ , 199 mV (Fig. 4). Restoration to the stand-by conditions shifts the latching point back to  $\bf A$ , 246 mV. The corresponding time diagram of write and read cycles is given in Fig. 5. Slight discrepancies between the values from I-V curves and transient diagram is due to parasitic resistance present in the test setup.

In conclusion, a prototype of Si/SiGe RITD-based T-SRAM has been presented. Load line analysis is performed to understand the latching mechanisms during the write and read cycles. This demonstration will lead to realization of fully-integrated Si/SiGe RITD/NMOS T-SRAM. Ultra-low power tunneling SRAM can be achieved by utilizing low current density RITDs.

## References

- [1] E. Goto, K. Mutara, K. Nakazawa, T. Moto-Oka, Y. Matsuoka, Y. Ishibashi, T. Soma, and E. Wada, "Esaki diode high-speed logical circuits," *IRE Trans. Electron. Comput.*, vol. 9, pp. 25–29, Mar. 1960.

- [2] J.P.A. Van der Wagt, "Tunneling-based SRAM," Proc. of IEEE, vol. 87, pp. 571-595, April 1999.

- [3] K. Morimoto, H. Sorada, and K. Morita, "Monolithic integration of Si-interband tunneling diodes with a MOSFET for ultralow voltage operation static random access memory," Future Elec. Dev., vol.11 Supplement, 2000.

- [4] S. Sudirgo, R.P. Nandgaonkar, B. Curanovic, J.L. Hebding, R.L. Saxer, S.S. Islam, K.D. Hirschman, S.L. Rommel, S.K. Kurinec, P.E. Thompson, N. Jin, and P.R. Berger, "Monolithically Integrated Si/SiGe Resonant Interband Tunnel Diode/CMOS Demonstrating Low Voltage MOBILE Operation," Solid-State Electronics, vol. 48, issues 10-11, pp. 1907-1910, Oct.-Nov., 2004.

- [5] N. Jin, S.-Y. Chung, A. T. Rice, P. R. Berger, P. E. Thompson, C. Rivas, R. Lake, S. Sudirgo, J. J. Kempisty, B. Curanovic, S. L. Rommel, K. D. Hirschman, S. K. Kurinec, P. H. Chi and D. S. Simons, "Diffusion Barrier Cladding in Si/SiGe Resonant Interband Tunneling Diodes And Their Patterned Growth on PMOS Source/Drain Regions," Special Issue on "Nanoelectronics" in IEEE Transactions on Electron Devices, vol. 50, pp. 1876-1884, Sept. 2003.

**Fig. 1** Circuit diagram of (a) T-SRAM cell; (b) during stand-by mode; (c) during the write to logic high (WH) cycle; (d) during the write to logic low (WL) cycle.

Fig. 2 Load line analysis of T-SRAM cell during stand-by (SB) mode, illustrating two latching points.

**Fig. 3** Load line analysis during write to logic high (WH) cycle, from point **A** to **B** to **C**.

**Fig. 4** Load line analysis during write to logic low (WL) cycle, from point **C** to **D** to **A**.

**Fig. 5** Time response diagram of T-SRAM at different stages of read and write cycles.